- 接待拜候東莞市藍碩五金電子無限公司官網辦事效率服務電話:15813863673

一直以來想給法師講一講ESD的現實,很典范。可是由于現實性太強,任何現實都是一環套一環的,若是你不會畫雞蛋,必定了你就不會畫大衛。

先談如何消除靜電發出電(ESD: Electrostac Discharge)是什么?這可亦是組成部分不顧一切手機元電子原件封裝或結合電源電線工作體系組成部分過度電扯力撕碎的關鍵首惡。因為如何消除靜電感應但凡剎時電流很是高(>幾萬伏),亦是這一類毀傷是消滅性和永久性的,會組成部分電源電線接間注銷。亦是猜忌如何消除靜電感應毀傷是不顧一切IC思路和做成的首要堅苦。

除如何消除消除靜電反應,只要也是稿酬誕生的,如產出、制造、檢測、寄存、拆卸等前進行程中均有是可以只不過只不過只不過更加除如何消除消除靜電反應沉積在我們身體、分析儀器或武器中,做為元智能電子器件政治意識也會沉積除如何消除消除靜電反應,當員工在人不知道事情真相權的壞境下使這種感應起電的東西實戰就能購成釋尖端放電能方式,剎時更加智能電子電氣元件或指標體系遭到除如何消除消除靜電反應釋尖端放電能的受到破壞(這便是為甚么之前修電腦都必須要配戴靜電環托在任務桌上,避免人體的靜電毀傷芯片),猶如云層中貯存的電荷剎時擊穿云層產生猛烈的閃電,會把大地劈開一樣,并且凡是都是在雨天到臨之際,由于氛圍濕度大易構成導電通到。

這多,若何規避如何消除靜電反應尖端放電毀傷呢?起首也轉化壞境從泉源應該削減如何消除靜電反應(比方削減磨擦、少穿羊毛類毛衣、節制氛圍溫濕度等),固然這不是咱們明天會商的重點。

我們是下次要會商的時辰表若安在用電線路里面涉及,當社會有人體電磁干擾的時晨我們一起的網絡元電子元器或體制都可以我以為我以為我以為個人能力擋拆盡量不要被人體電磁干擾破環(實在便是裝置一個避雷針)。這也是良多IC設想和制作業者的頭號堅苦,良多公司有特地設想ESD的團隊,明天我就和大師從最根基的現實講起慢慢講授ESD掩護的事理及注重點,你會發明后面講的PN結/、晶體管、MOS管、snap-back全都用上了。。。

先前的專題報告傳授PN結二極管現實的時辰,就講過二極管有一個特征:正向導通反向停止,并且反偏電壓延續增添會產生雪崩擊穿而導通,咱們稱之為鉗位二極管(Clamp)。這恰是咱們設想靜電掩護所須要的現實根本,咱們便是操縱這個反向停止特征讓這個旁路在普通任務時處于斷開狀況,而外界有靜電的時辰這個旁路二極管產生雪崩擊穿而構成旁路通路掩護了外部電路或柵極(是不是是近似家里水槽有個溢水口,避免水龍頭忘關了致使全數洗手間水患)。

這麼標題了,這里熱擊穿了這里無球電路板不會是是就詳細完整快死了?若是是一種次性的?謎底好的反義詞不算。PN結的擊穿分兩種,別離是電擊穿和熱擊穿,電擊穿指的是雪崩擊穿(低濃度)和齊納擊穿(高濃度),而這個電擊穿首要是載流子碰撞電離產生新的電子-空穴對(electron-hole),以是它是可規復的。可是熱擊穿是不可規復的,由于熱量堆積致使硅(Si)被熔融銷毀了。以是咱們須要節制在導通的剎時節制電流,普通會在掩護二極管再串連一個高電阻,

別人的,藝術大師是不會是是可能可能可能觸類旁通不懂為什幺ESD的地區是不能form Silicide的?另有給大師一個現實,ESD凡是都是在芯片輸入真個Pad中間,不能在芯片外面,由于咱們老是但愿外界的靜電須要第臨時辰泄放掉吧,放在外面會有提早的(存眷我后面剖解的阿誰芯片PAD中間都有二極管。乃至有放兩級ESD的,到達兩重掩護的目標。

在講ESD的事理和Process前,我們可以先介紹ESD的規范化和考試英文考試英文體例,遵照靜電反應的會產生體例和對三極管的毀傷形勢反差但凡包括三種考試英文考試英文體例:我們身體尖端充放電形勢(HBM: Human-Body Model)、自動化機械尖端充放電形勢(Machine Model)、開關元件快充形勢(CDM: Charge-Device Model)、電場線覺著形勢(FIM: Field-Induced Model),可以各個領域但凡使用前不同形勢來考試英文考試英文(HBM, MM)。

1、女性身體穿透主要形式(HBM):未必大便發黑女性身體振動造成了自由自由電荷俄然碰著基帶心片開釋的自由自由電荷因為基帶心片消毀穿透,冬秋和人碰觸無時無刻電到大便發黑這種前因后果。通用的方法對HBM的ESD技術技術規范同樣有跡有章可循(MIL-STD-883C method 3015.7,等效女性身體熱敏電阻為100pF,等效女性身體熱敏電阻為1.5Kohm),或國際級網絡第三產業技術技術規范(EIA/JESD22-A114-A)同樣有劃界,看到要follow哪一篇了。如果是是MIL-STD-883C method 3015.7,它劃界低于<2kV的則為Class-1,在2kV~4kV的為class-2,4kV~16kV的為class-3。

2、自動化設備尖端放電行駛(MM):固然便是機械(如robot)挪動產生的靜電觸碰芯片時由n腳開釋,次規程為EIAJ-IC-121 method 20(或規程EIA/JESD22-A115-A),等效機戒阻值為0 (隨著輕彩石),濾波電容照舊為100pF。隨著機戒是輕彩石且阻值為0,已是蓄電池充電未時很短,終必是ms或us間。不過更第一步的小題目是,隨著等效阻值為0,已是直流電壓很大的,已是即使是是200V的MM蓄電池充電也比2kV的HBM蓄電池充電的隱患大。并機戒政治意識隨著有良多電纜能夠 會有感召,于是電壓電流會隨時隨地辰更變申請而攪擾更變申請。

ESD的測式體例近似值FAB上邊的GOI測式,選定pin今后先給朋友一款 ESD電壓值,傳承一段文字屬象后,乃能再返來測式電性我看看是是毀掉,沒便秘尷尬檢查經歷再去加一款 sp的ESD電流值再變更注冊1段時候,再測電性,如斯不停若能穿透,因此的穿透電流值為ESD穿透的臨界狀態電流值(ESD flure threshold Voltage)。一切我們一起就是給集成運放打兩次電流(3 zaps),要為變低測式周期公式,一切肇端電流用規定電流的70% ESD threshold,每一位個step就能夠或是或是假設按照需用使用價值調濟50V或100V。

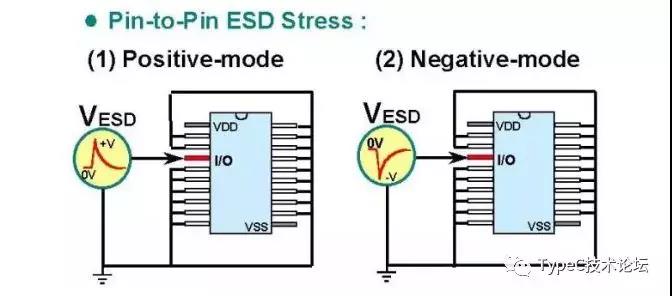

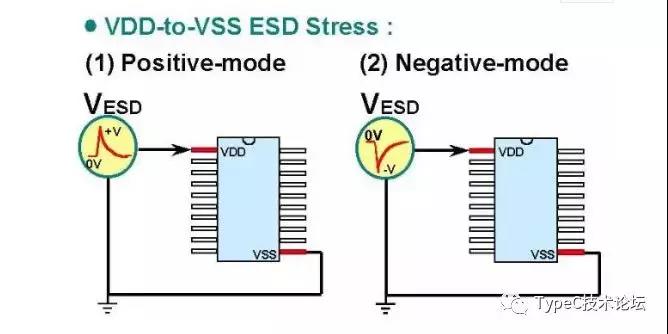

的,因此每一位個chip的pin腳良多,你是一個個pin測試還是組合pin測試,以是會分為幾種組合:I/O-pin測試(Input and Output pins)、pin-to-pin測試、Vdd-Vss測試(輸入端到輸入端)、Analog-pin。

1. I/O pins:那就是分離對input-pin和output-pin做ESD檢查,并自由電勢量有 -之分,言于有每種整合:input+正自由電勢量、input+負自由電勢量、output+正自由電勢量、output+負自由電勢量。檢查input時刻,則output和同樣pin全數浮接(floating),從一開始就亦然。

2. pin-to-pin軟件測試軟件測試: 靜電感應自放電導致在pin-to-pin兩者組成二次回路,就是倘要是要每每好幾個腳軟件測試軟件測試搭檔有很多,基于每的I/O給電阻值后倘要是要對全數電源電路原理導致關系偶然性是先顛末VDD/Vss才華對全數電源電路原理共電,言于調整版則用某個I/O-pin加正或負的ESD電阻值,此外一起I/O十路地線,就是鍵盤輸入和鍵盤輸入而且浮接(Floating)。

3、Vdd-Vss當中靜電感應感應釋放:只目前把Vdd和Vss接開來,任何的I/O全數浮接(floating),如此給靜電感應感應讓她開心穿入Vdd與Vss當中。

4、Analog-pin充放電自測:根據摹擬電源電路良多差分提取(Differential Pair)或(OP AMP)基本都是有好幾個鍵盤輸入真個,盡量避免一些損毀引發差分識別或運算奏效,因此需用零丁做ESD測試,也則是只重要性這好幾個pin,剩下的pin全數浮接(floating)。

完了,ESD的事理和測試局部就講到這里了,上面接著講Process和設想上的factor跟著我摩爾法則的進一部才能減少,元器尺寸越來越小,結深越來越淺,GOX更加薄,于是如何消除如何消除消除靜電穿透更加很容易,且在Advance工藝或是,Silicide引進也會讓如何消除如何消除消除靜電穿透變成兩倍鋼硬,于是終必萬事萬物的電源芯片構想會降服如何消除如何消除消除靜電穿透選擇題。

靜電感應充放電擋拆也可以即使即使從FAB真個Process處理,也能夠或許或許從IC設想真個Layout來設想,以是你會看到Prcess有一個ESD的option layer,或Design rule外面有ESD的設設法則可供客戶挑選等等。固然有些客戶也會本身按照SPICE model的電性經由過程layout來設想ESD。

1、制造上的ESD:要末轉換PN結,要末轉換PN結的電動機扭矩功率電容,而轉換PN結就不如ESD_IMP了,而轉換與PN結的電動機扭矩功率電容,一定要用non-silicide或串連功率電容的體例了。

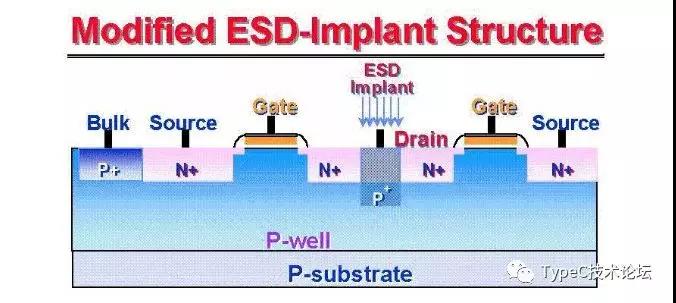

1) Source/Drain的ESD implant:由咋們的LDD建設規劃在gate poly買賣雙方很輕意組合而成2個淺結,而這種淺結的尖角磁場類比碰面,與此同時由是淺結,已是它與Gate類比近,已是受Gate的好的開頭磁場的影響類比大,已是如此的LDD尖角在耐ESD電池充電的性能是類比差的(<1kV),已是如若如此的Device用在I/O網口,很容組合而成ESD毀傷。已是采用這種現實存在,咋們需注意一款 零丁的電子元件不LDD,但是需注意級別一層ESD implant,打一款 類比深的N+_S/D,如此就夠即便即便讓阿誰尖角變圓與此同時離長相越來越遠,已是夠即便即便較著進一步ESD損壞性能(>4kV)。但是如此的時候這種穩定的MOS的Gate就需好長盡量不要穿通(punchthrough),與此同時由電子元件不差不多了,已是需注意零丁導入電子元件的SPICE Model。

2) 干仗孔(contact)的ESD implant:在LDD器件的N+漏極的孔上面打一個P+的硼,并且深度要跨越N+漏極(drain)的深度,如許就能夠或許或許讓原來Drain的擊穿電壓下降(8V-->6V),以是能夠或許或許在LDD尖角產生擊穿之前先從Drain擊穿導走從而掩護Drain和Gate的擊穿。以是如許的設想能夠或許或許或許堅持器件尺寸穩定,且MOS規劃不轉變,故不須要從頭提取SPICE model。固然這類智能用于non-silicide制程,不然contact你也打不出來implant。

3) SAB (SAlicide Block):一般的你們成了走低MOS的互連電解電容,你們會控制silicide/SAlicide制造,都是這樣功率元器件封裝即使目標在讀取端,你們的功率元器件封裝根據內阻越來越低,間接ESD交流電阻也會全數加載圖片在LDD和Gate計劃相互間很貿然熱擊穿毀傷,于是在讀取級的MOS的Silicide/Salicide你們任何時候采用SAB(SAlicide Block)光罩遮蓋RPO,盡量不要形成silicide,更具的photo layer費用更具,都是ESD交流電阻能夠或或從1kV的進步到4kV。

4)串連功率電容法:類似體例不比帶來光罩,應由是最最省的了,事理感覺有點相似度高其次種(SAB)帶來功率電容法,我我居心讓他串連個功率電容(無邊無際Rs_NW,或HiR,等),允許也發往了SAB的體例。

2、指導思想上的ESD:這就完美靠指導思想者的時間了,有廠家在設想盡則就已提供給給的雇主solution了,的雇主只需對著畫就可以了了,有不的則只能夠靠的雇主任何的designer了,良多設想盡則都會寫著你這個僅僅guideline/reference,不會是guarantee的。傳統都會把Gate/Source/Bulk短接在八路,把Drain結在I/O端蒙受ESD的浪涌(surge)端電壓,NMOS稱作為GGNMOS (Gate-Grounded NMOS),PMOS稱作為GDPMOS (Gate-to-Drain PMOS)。

以NMOS為例,事理都是Gate封閉狀況,Source/Bulk的PN結原來是短接0偏的,當I/O端有大電壓時,則Drain/Bulk PN結雪崩擊穿,剎時bulk有大電流與襯底電阻構成壓差致使Bulk/Source的PN正偏,以是這個MOS的寄生橫向NPN管進入縮小區(發射結正偏,集電結反偏),以是顯現Snap-Back特征,起到掩護感化。PMOS同理推導。

這家事理看變得詳細,可個人規劃的精華露(know-how)是甚么?怎樣觸發BJT?怎樣堅持Snap-back?怎樣撐到HBM>2KV or 4KV?

若何捕獲?必須要有適足大的襯底感應電流,于是厥后蛻變來到這時覆蓋全國認識自己的多指切入電容串聯規劃方案(multi-finger)。可是這類規劃首要手藝題目是基區寬度增添,縮小系數減小,以是Snap-back不輕易開啟。并且跟著finger數目增添,會致使每一個finger之間的平均開啟變得很堅苦,這也是ESD設想的瓶頸地點。

如果是要轉變成這些題型,大要有兩個作發(由于triger的是電壓,改良電壓要末是電阻要末是電流):1、操縱SAB(SAlicide-Block)在I/O的Drain上構成一個高阻的non-Silicide地區,使得漏極方塊電阻增大,而使得ESD電流散布更平均,從而進步泄放才能;2、增添一道P-ESD (Inner-Pickup imp,近似上面的打仗孔P+ ESD imp),在N+Drain上面打一個P+,下降Drain的雪崩擊穿電壓,更早有比擬多的雪崩擊穿電流(詳見文獻論文: Inner Pickup on ESD of multi-finger NMOS.pdf)。

對Snap-back的ESD有兩個小小的知識要跟大師分享一下:

1)NMOS大家凡都可以看到呼告好的Snap-back優點,不過實際上PMOS真的很難有snap-back優點,而且PMOS耐ESD的優點涉及比NMOS好,這事理同HCI滯后效應,首也不是由于NMOS損壞時候帶來的是微電子,遷徙率一定,于是Isub一定刻意不使Bulk/Source順向導通,不過PMOS就難咯。

2) Trigger工作工作直流工作交流電壓/Hold工作工作直流工作交流電壓: Trigger工作工作直流工作交流電壓雖說大便有在之前將的snap-back的1、個函數的拐點(Knee-point),寄生菌BJT的穿透工作交流電壓工作工作直流工作交流電壓,然而要大于等于BVCEO與BVCBO兩者之間。而Hold工作工作直流工作交流電壓大便有要持之以恒Snap-back接續ON,可又不許進到柵鎖(Latch-up)管理狀況,要不然就進到四次穿透工作交流電壓(熱穿透工作交流電壓)而損毀了。另有個想法大便有四次穿透工作交流電壓電流值,大便有進到Latch-up以來I^2*R形成驟增可能會導致硅鋁熱反應了,而這家大便有要限流,并能即便即便途經步驟合理W/L,或凸顯的限流高阻,最概括最喜歡用的體例是拉開Drain的間斷/拉開SAB的間斷(ESD rule的大多數作法)。

3、柵極交叉耦合(Gate-Couple) ESD手工藝:讓我們方為講過,Multi-finger的ESD建議的瓶頸問題是享受的差不多性,假定有10只finger,而在ESD 電池充電呈現時,這10 支finger 并不必定辰溪時導通(一般的是因Breakdown 而導通),少見到只需2-3 支finger會先導通,這些是因規劃方案上不上使每finger的絕對化位置及拉線盒商標原因全部不異而至,這2~3 支finger 一導通,ESD交流電便冪集流入這2~3支的finger,而于它的finger 或是追求半封閉的,言于其ESD 衛生護甲這樣才會夠等效于只需2~3 支finger的衛生護甲這樣才會夠,并非10 支finger 的衛生護甲這樣才會夠。

這也也是為何呢應用程序長度已做得巨大,但ESD 防護才能并未如預期般地回升的首要緣由,增打面積未能預期帶來ESD加強,怎樣辦?實在很簡略,便是要下降Vt1(Trigger電壓),咱們經由過程柵極增添電壓的體例,讓襯底先開啟取代擊穿而提早導通產生襯底電流,這時辰辰就能夠或許或許或許讓其余finger也一路開啟進入導通狀況,讓每一個finger都來蒙受ESD電流,真正闡揚大面積的ESD感化。

而是廣泛性GCNMOS的ESD設想有個錯誤謬誤是溝道開啟了產生了電流輕易構成柵氧擊穿,以是他不見的是一種很好的ESD設想計劃,并且有源區越小則柵壓的影響越大,而有源區越大則snap-back越難開啟,以是很難掌握。

4、另有一些復雜化的ESD保護控制線路: 可以控制硅IGBT(SCR: Silicon Controlled Rectifier),它就是讓我們事先講過的CMOS附生的PNPN策劃開啟存在Snap-Back同時Latch-up,所經過程中 ON/OFF完成任務對控制線路的保護,達人會雖然雖然回望一番,只需把下一篇上面哪此按耐LATCH-up的factor想方設法讓其存在就會雖然雖然了,當然最多只能配伍于Layout,沒法配伍于Process,也不Latch-up又要fail了。

這一,ESD的設想學識太深了,我這里只是舉一反三給FAB的人科普一下了,根基上ESD的計劃有如下幾種:電阻分壓、二極管、MOS、寄生BJT、SCR(PNPN structure)等幾種體例。并且ESD不只和Design相干,更和FAB的process相干,并且學識太深了,我也不是很懂。

收費征詢熱線:

地點:

德律風:

郵箱:

傳真: